如何使用示波器解決LCD控制器調試難題

當LCD液晶屏顯示異常時,以往通過現象逆向推導,對參數進行修改,這種方式費時費力。有了長存儲示波器,調試LCD控制器再也不燒腦,下文通過實際案例分享ZDS4054Plus在LCD測試中的應用。

一、LCD控制器、驅動器工作原理

要使LCD的顯示文字或圖像,需要通過LCD控制器輸出RGB數據給LCD驅動器,LCD驅動器就把數據放到緩存中,然后以60幀/秒的速度刷新LCD屏顯示。(由于液晶分子的特性:當長時間固定在某一個電壓不變時,會導致液晶分子遭到破壞,所以要以一定的頻率(通常是60Hz)不停的刷新LCD屏。所以視頻播放幀率雖然只有23~30幀/秒,TFT-LCD的顯示刷新頻率卻達到60Hz。LCD控制器時序控制著視頻幀率;LCD驅動器時序控制著顯示器刷新率。)

LCD控制器器通過行信號和列信號的不同組合,實現對每個像素進行控制,這種行掃描(HYNC)信號周期很短(高達40kHz-100kHz),使屏幕上能夠顯示穩定的圖像。

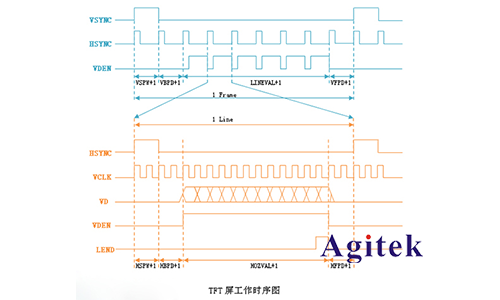

LCD控制器信號時序及工作原理如下:

VSYNC:幀同步信號,表示掃描1幀的開始,一幀也就是LCD顯示的一個畫面;

HSYNC:行同步信號,表示掃描1行的開始;

VCLK:像素時鐘信號,每個脈沖填充1個像素點;

VDEN:數據使能信號,高電平時,填充數據有效;

VD[23:0]:LCD像素數據輸出端口。

LEND:行結束信號;

以一個1024X768像素的LCD屏為例,完整顯示一屏圖像的信號,必須包含1個VSYNC周期、768個有效HSYNC周期,每個VDEN高電平包含1024個像素時鐘信號。顯示出現問題可通過幀同步信號、行同步信號的頻率、占空比、延時、每個VSYNC周期包含的HSYNC周期數、VDEN周期包含的VSCLK周期數進行排查。

二、使用ZDS4054Plus示波器解決LCD顯示異常實例

1、圖片疊加、重復

現象:LCD顯示上大范圍的圖像出現錯位、疊加或者重復;

成因:出現這種情況一般不會是行同步或者場同步信號的延時引起的,基本可以排除這方面的影響。可以檢查是否存在時序或者時鐘頻率上存在差異引起的。

解決方法:碰見這種情況首先應該做的就是先仔細計算DMA傳輸參數,精確適配行場信號。

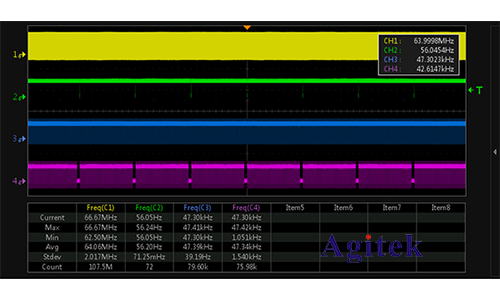

如示波器截圖所示,各通道對應信號依次為VCLK、VSYNC、VHSYNC、VDEN信號,分析步驟如下:

1)由于一幀完整的信號時間通常達到30ms以上,示波器需要調到10ms/div的時基,而VCLK信號頻率通常高達48-96MHz,采樣率至少得保持500Ms/s,才能對時序進行分析,此時普通示波器無法完整捕獲波形。

2)ZDS4054Plus在10ms/div的時基下,依然能夠保持1Gs/s采樣率,可完美還原波形,配合每通道標配的硬件頻率計,可分析各信號頻率是否存在異常;

2、圖像錯位

現象:LCD顯示在水平方向發生位移,或者在上面或底部有一條幾個像素的彩色、白色或黑色條紋。

原因:一般來說,出現這種情況和幀同步、行同步信號有關,如果是常態異常,可能是初始化參數設置不對,若是偶發異常可能是工作過程中,幀同步、行同步信號收到干擾。

解決方法:檢查LCD控制器的行同步與場同步信號的寬度、前后延時、極性的匹配。

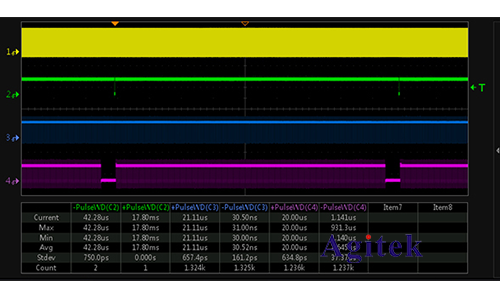

如示波器截圖所示,各通道對應信號依次為VCLK、VSYNC、VHSYNC、VDEN信號,分析步驟如下:

1)通過全屏測量統計,分析各信號正負脈沖寬度,若VSYNC、VHSYNC脈寬存在異常值,可判斷為干擾信號引起的顯示異常;

2)若脈寬正常時,可通過區間測量統計計算周期數,分析各個大小周期信號直接的相互包含關系,檢查時序參數;

3)通過縮放模式以及光標測量,分析各時序信號之間的延時。

以上就是如何使用示波器解決LCD控制器調試難題的相關介紹,如果您有更多疑問或需求可以關注西安安泰測試Agitek哦!非常榮幸為您排憂解難。

技術支持

關注官方微信

關注官方微信